DDR4 초기화와 메모리 트레이닝의 비밀: 왜 오픈소스 펌웨어는 아직도 고통받는가

서버 전원 버튼을 누르고 OS가 부팅되기까지의 몇 초. 우리 같은 엔지니어들은 종종 이 짧은 시간을 당연하게 여긴다. CPU가 리셋 벡터를 읽고 커널을 올린다고 단순하게 생각하지만, 사실 그 이면에는 엄청나게 복잡한 아날로그와 디지털의 춤사위가 숨어 있다. 특히 메모리 하위 시스템이 그렇다.

최근 Hacker News에서 DDR4 초기화 및 캘리브레이션에 대한 훌륭한 시스템베릴로그(SystemVerilog) 블로그 글이 화제가 되었다. 15년 넘게 시스템 엔지니어링을 해오면서 수많은 보드 브링업(Bring-up)을 경험했지만, 메모리 트레이닝은 늘 블랙박스처럼 느껴지던 영역이다. 오늘은 이 글을 바탕으로 DDR4가 어떻게 깨어나는지 기술적으로 딥다이브해보고, 왜 이 과정이 철저한 영업 비밀로 취급되어 오픈소스 펌웨어 생태계를 고통받게 하는지 내 생각을 정리해 보려 한다.

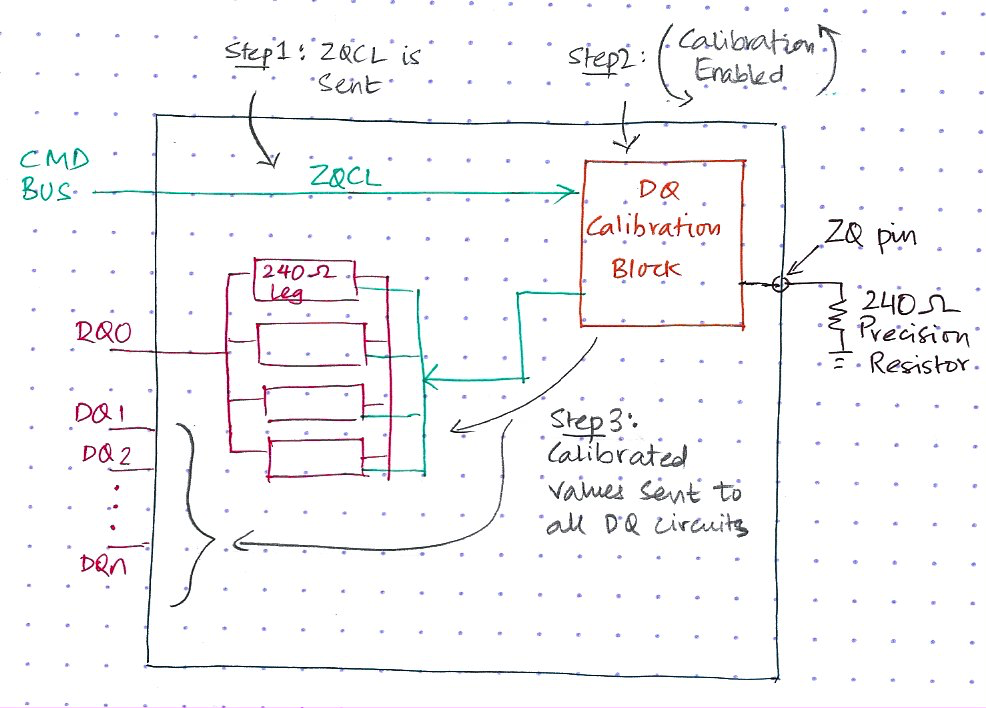

ZQ Calibration: 아날로그의 불확실성을 통제하다

DDR4에 전원이 인가되고 클럭이 활성화되면, 가장 먼저 마주하는 핵심 단계 중 하나가 ZQ Calibration이다.

초보 엔지니어들은 디지털 신호를 완벽한 0과 1의 구형파로 생각하지만, 고속 신호의 세계에서 DQ 핀은 철저히 아날로그적으로 동작한다. DRAM 내부의 DQ 핀 뒤에는 240Ω의 폴리 실리콘 저항 네트워크가 병렬로 연결되어 있다. 문제는 CMOS 공정의 특성상 이 저항값이 온도나 전압에 따라 끊임없이 변한다는 것이다.

이를 해결하기 위해 외부에 정밀도 1%짜리 240Ω 레퍼런스 저항을 ZQ 핀에 연결한다. 초기화 시 ZQCL 커맨드가 떨어지면, 내부 비교기가 VDDq/2 전압을 맞출 때까지 트랜지스터들을 튜닝한다. 이 과정을 통해 Drive Strength(Read)와 Termination Resistance(Write)를 정확히 맞춘다. PCB 라우팅마다 달라지는 임피던스를 보정해 신호 무결성을 확보하는 첫 단추인 셈이다.

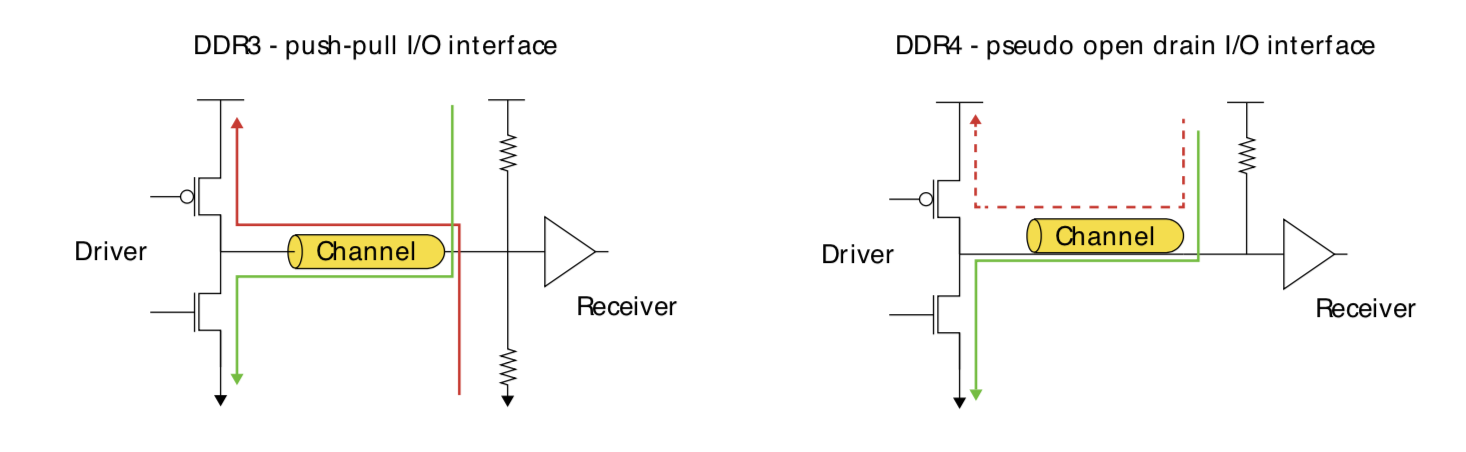

Vref DQ Calibration: DDR3의 SSTL에서 DDR4의 POD로

개인적으로 DDR4 스펙을 처음 읽었을 때 가장 흥미로웠던 부분이다. DDR3는 데이터 라인 종단에 CTT(Center Tapped Termination, 또는 SSTL) 방식을 사용해 Vdd/2를 레퍼런스 전압으로 삼았다.

하지만 DDR4는 전력 소모를 줄이고 고속 신호 무결성을 확보하기 위해 POD(Pseudo Open Drain) 방식을 채택했다. (GDDR5에서 이미 증명된 방식이기도 하다). 수신단에 전압 분배 회로를 두는 대신, DRAM 내부에 VrefDQ라는 자체 전압 레퍼런스를 생성한다. 메모리 컨트롤러는 캘리브레이션 단계에서 이 VrefDQ 값을 모드 레지스터(MR6)를 통해 정확하게 세팅해야 한다.

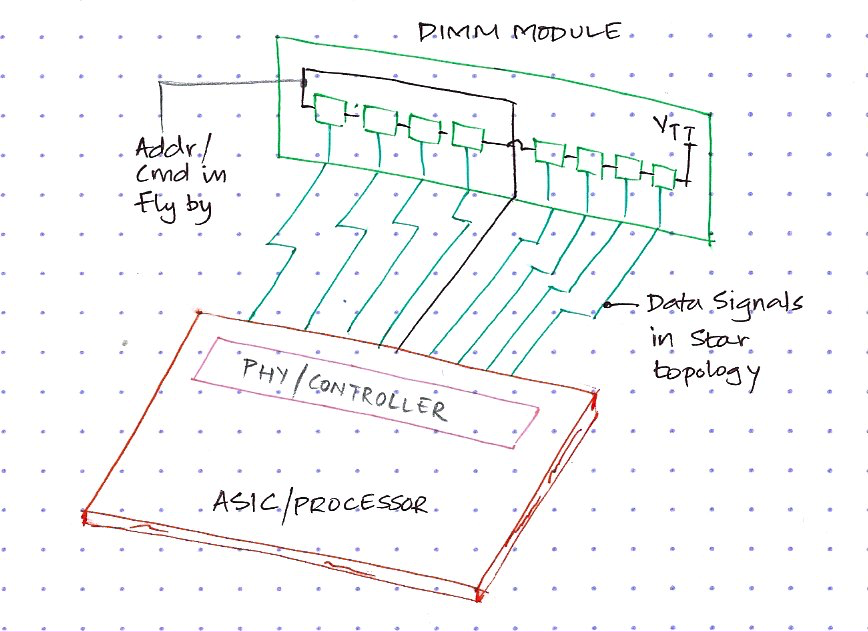

Fly-by Topology와 Read/Write Training의 악몽

초기화가 끝나고 DRAM이 IDLE 상태에 진입했다고 해서 바로 데이터를 읽고 쓸 수 있는 것은 아니다. 진짜 마법은 이제부터 시작된다.

과거에는 메모리 칩들을 Star Topology로 연결했지만, 고속 동작을 위해 DDR3부터는 Clock, Command, Address 라인을 데이지 체인처럼 엮는 Fly-by routing을 사용한다. 신호 무결성은 좋아졌지만, 치명적인 부작용이 생겼다. CPU 입장에서 DIMM 모듈에 박힌 각 DRAM 칩까지의 물리적 거리가 모두 달라진 것이다.

즉, 클럭과 데이터 스트로브(DQS) 사이의 Skew가 칩마다 제각각이다. 이를 보정하기 위해 컨트롤러는 다음의 알고리즘들을 수행한다.

- Write Leveling: tDQSS 타이밍을 맞추기 위한 과정이다. 컨트롤러가 DQS 펄스를 쏘면 DRAM은 이를 이용해 CK를 샘플링하고 결과를 DQ로 반환한다. 컨트롤러는 0에서 1로 변하는 트랜지션 포인트를 찾을 때까지 딜레이를 조절한다.

- MPR Pattern Write: 본격적인 Centering에 앞서 DRAM 내부의 8비트 레지스터(MPR)에 특정 패턴을 미리 써두는 과정이다.

- Read/Write Centering: 데이터 아이(Data Eye)의 정중앙을 찾는 과정이다. 앞서 쓴 패턴(예: 1-0-1-0)을 계속 읽어들이면서 내부 딜레이를 좌우로 스윕(Sweep)해 완벽한 타이밍 윈도우를 찾는다.

Hacker News Context & My Perspective: 왜 우리는 이 코드를 볼 수 없는가?

Hacker News 스레드에서 가장 뜨거웠던 논쟁은 바로 “왜 이 트레이닝 코드는 철저한 블랙박스인가?” 였다. 한 유저의 지적처럼, 메모리 트레이닝은 메모리 제조사와 EDA IP 벤더들의 핵심 영업 비밀이다.

현업에서 일해보면 이게 얼마나 뼈저린 문제인지 알 수 있다. Coreboot 같은 오픈소스 펌웨어 프로젝트가 항상 부딪히는 벽이 바로 Intel FSP나 AMD AGESA 같은 바이너리 블랍(Blob)이다. 실리콘 벤더들은 메모리 컨트롤러 IP를 외부에서 사오고, 이 IP를 초기화하는 코드는 NDA로 굳게 묶여 있다.

솔직히 말해서, “그냥 JEDEC 스펙 문서 보고 짜면 되는 거 아니냐?”라고 묻는다면, 현실은 스펙 문서 밖의 수많은 매직 넘버와 실리콘 버그 워크어라운드가 존재한다는 것이다. 보드 라우팅의 미세한 차이, 특정 주차에 생산된 DRAM의 수율 문제 등을 커버하기 위한 수백만 줄의 코드가 그 블랍 안에 들어있다.

제조사 입장에서 칩의 안정성을 보장하기 위해 코드를 닫아두는 것은 기업의 이윤 추구 관점에서 이해가 간다. 하지만 시스템을 극한까지 튜닝하고 엣지 케이스를 디버깅해야 하는 엔지니어 입장에서는, 간헐적인 커널 패닉의 원인이 메모리 트레이닝 실패인지 OS 버그인지 추적할 수 없을 때 극도의 무력감을 느낀다. 하드웨어 디버깅의 가장 중요한 도구를 빼앗긴 기분이랄까.

Verdict

DDR4(그리고 현재의 DDR5)의 초기화 및 캘리브레이션 과정은 현대 아날로그/디지털 혼성 설계의 극치다. 1초도 안 되는 시간에 수기가헤르츠의 신호 무결성을 스스로 튜닝하는 이 시스템은 경이롭기까지 하다.

하지만 하드웨어 생태계가 점점 더 폐쇄적인 IP 블록과 바이너리 블랍에 의존하는 방향으로 흘러가는 것은 엔지니어로서 씁쓸하다. 시스템의 가장 밑바닥을 이루는 메모리 초기화 과정이 소수의 벤더에게 독점되는 한, 진정한 의미의 완벽한 오픈 하드웨어 생태계는 아직 요원해 보인다. 우리가 매일 사용하는 서버와 랩탑은, 사실 우리가 완전히 통제하지 못하는 거대한 블랙박스 위에서 돌아가고 있는 셈이다.

References

- Original Article: DDR4 SDRAM – Initialization, Training and Calibration

- Hacker News Thread: News YCombinator